# Computer Architecture with (MIPS) Assembly

Peter Stallinga

peter@stallinga.org

Computer Architecture: with (MIPS) Assembly (paperback)

Peter Stallinga

v. 2.0 (November 26, 2024)

Copyright © 2024, Peter Stallinga. All rights reserved

ISBN: 978-1-31281-319-9

Typefaces: Times Roman, Helvetica, Free Sans Typesetting: IATEX2e with TexLive in TexMaker

Graphical: Inkscape and PjotrSoft. All pictures made by the author, except the photo used for the cover (Weber VanHeber) and Pictures 5 (adapted from Wikipedia), 6 (Wikipedia), 88 (output of MARS 4.5 of Sanderson and Vollmar), and 94 (Wikipedia).

stallinga.org

Non-profit science organization

### Contents

| 1 | Intr | $\operatorname{roduction}$                         |

|---|------|----------------------------------------------------|

| 2 | Nu   | mber systems                                       |

|   | 2.1  | Binary numbers                                     |

|   | 2.2  | Octal, hexadecimal and binary-coded decimal 18     |

|   | 2.3  | Arithmetic                                         |

|   | 2.4  | Number conversion                                  |

|   | 2.5  | Negative numbers                                   |

|   | 2.6  | ASCII                                              |

|   | 2.7  | Gray code                                          |

|   | 2.8  | Floating point                                     |

|   | 2.9  | Exercises                                          |

| 3 | Boo  | holean algebra/logic                               |

|   | 3.1  | Set theory and Boolean algebra                     |

|   | 3.2  | Huntington postulates                              |

|   | 3.3  | Formal derivation of the truth tables              |

|   | 3.4  | From postulates to truth tables                    |

|   | 3.5  | sum-of-products (SoP) and product-of-sums (PoS) 56 |

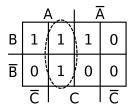

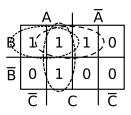

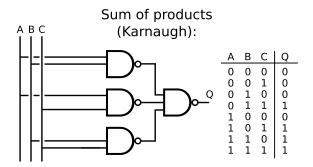

|   | 3.6  | Karnaugh maps                                      |

|   | 3.7  | Exercises                                          |

| 4 | Har  | dware components                                   |

| - | 4.1  | Electronics: from transistors to gates             |

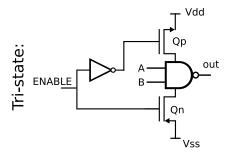

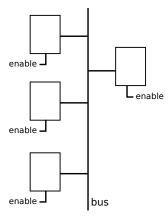

|   | 4.2  | Tri-state                                          |

|   | 4.3  | From gates to logic circuits                       |

|   | 4.4  | Karnaugh maps in electronics                       |

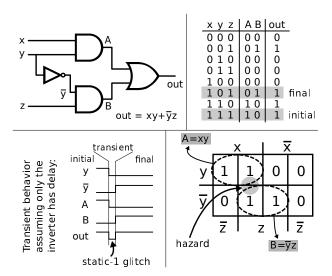

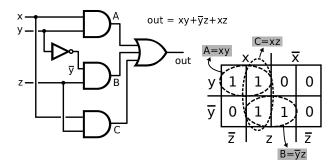

|   | 4.5  | Timing; transient behavior. Glitches and hazards   |

|   | 4.6  | Latches, flip-flops and memory                     |

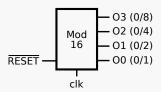

|   | 4.7  | Finite-state machines (FSMs)                       |

|   |      | 4.7.1 Moore machine sequencers                     |

|   |      | 4.7.2 Mealy machines                               |

|   | 4.8  | Exercises                                          |

iv CONTENTS

| 5  | Inte | gration                                                |   | . 109 |

|----|------|--------------------------------------------------------|---|-------|

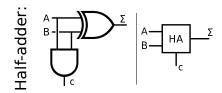

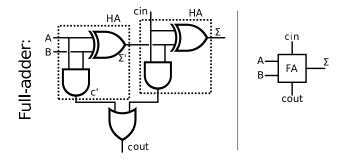

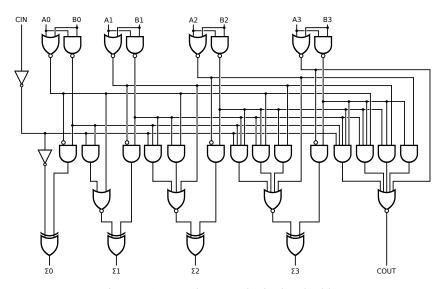

|    | 5.1  | Half-adder/full-adder                                  |   | . 109 |

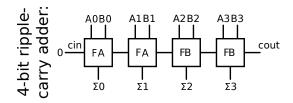

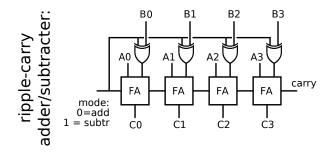

|    | 5.2  | Summing and subtracting                                |   | . 112 |

|    | 5.3  | Advanced adding and subtracting                        |   | . 114 |

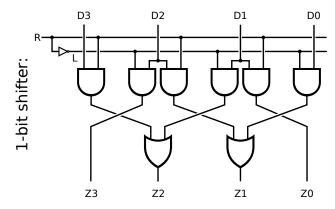

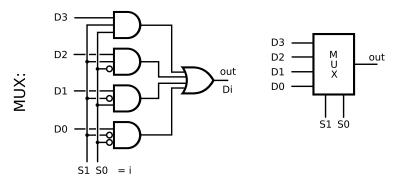

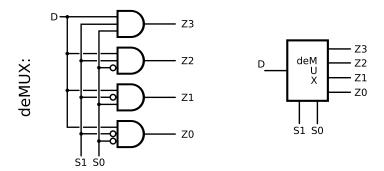

|    | 5.4  | Advanced logic circuits                                |   | . 114 |

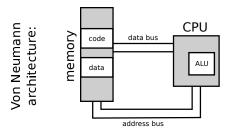

| 6  | Con  | aputers                                                |   | . 123 |

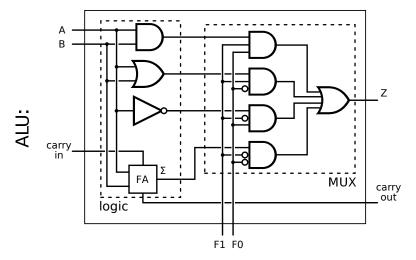

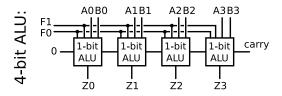

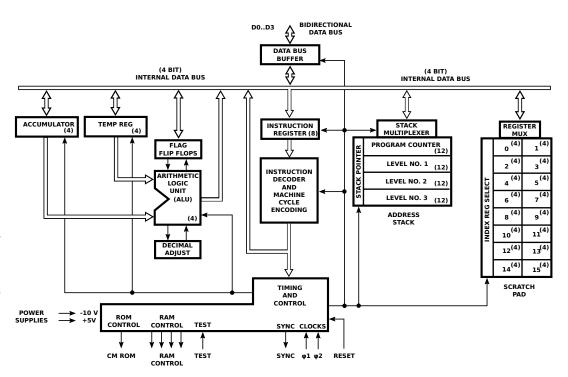

|    | 6.1  | Arithmetic and logic unit (ALU)                        |   | . 123 |

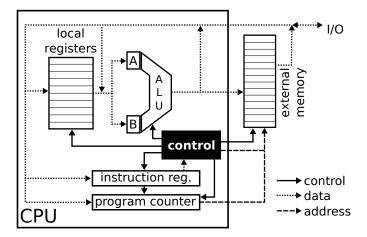

|    | 6.2  | Central processing unit (CPU)                          |   |       |

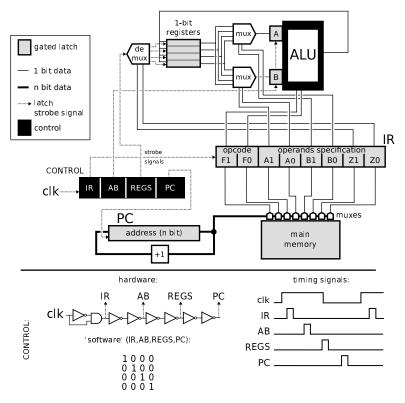

|    | 6.3  | Control logic                                          |   | . 126 |

|    | 6.4  | Programming the CPU                                    |   | . 129 |

|    | 6.5  | Advanced arithmetic: Multiplication and division       |   | . 130 |

|    | 6.6  | Floating point; IEEE 754                               |   | . 133 |

|    | 6.7  | Advanced calculations                                  |   | . 139 |

| 7  | Info | rmation and memory                                     |   | . 145 |

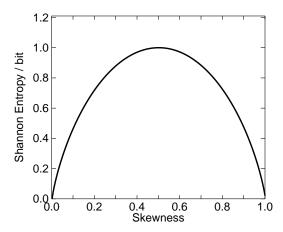

|    | 7.1  | (Quantifying) Information                              |   | . 146 |

|    | 7.2  | Information sizes                                      |   | . 151 |

|    | 7.3  | External memory                                        |   |       |

|    | 7.4  | Internal memory                                        |   | . 160 |

|    | 7.5  | Software aspects of memory                             |   | . 161 |

|    |      | 7.5.1 Heap and stack                                   |   | . 164 |

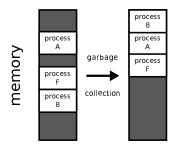

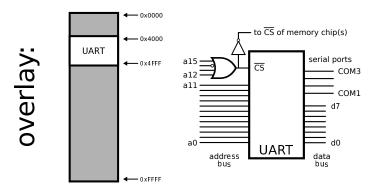

|    |      | 7.5.2 Garbage collection, paging, and overlays         |   |       |

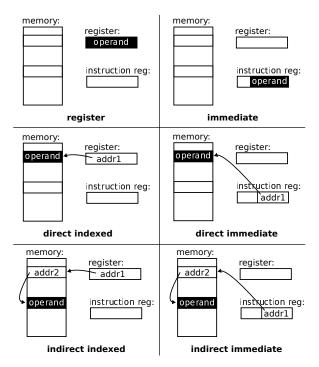

|    |      | 7.5.3 Addressing modes                                 | • | . 168 |

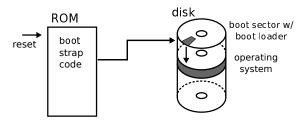

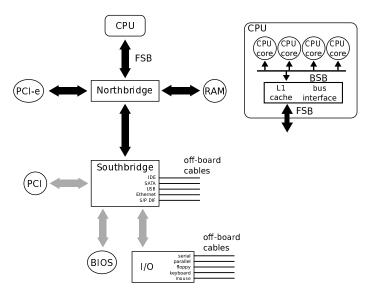

| 8  | Har  | $	ext{dware/software aspects} \dots \dots \dots \dots$ |   | . 171 |

|    | 8.1  | Interrupts                                             |   | . 172 |

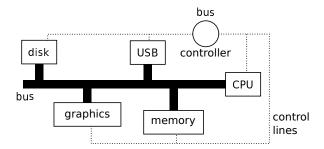

|    | 8.2  | Bus                                                    |   |       |

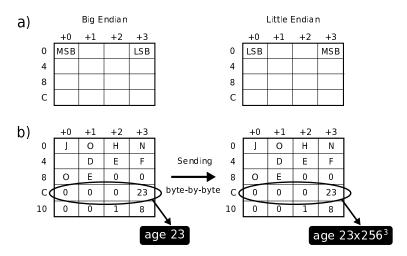

|    | 8.3  | $Communication \ . \ . \ . \ . \ . \ . \ . \ . \ . \ $ |   | . 176 |

| 9  | Arc  | hitecture of MIPS                                      |   | 179   |

|    |      |                                                        |   |       |

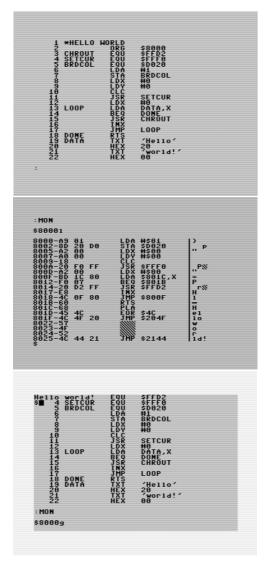

| 10 |      | RS: MIPS Assembly language implementation              |   |       |

|    |      | Input/output (system calls) and memory access          |   |       |

|    |      | Arithmetic                                             |   |       |

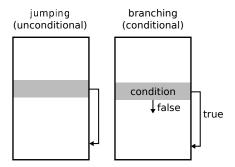

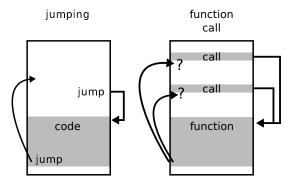

|    |      | Jump and branch; (goto, if then goto)                  |   |       |

|    |      | Loops; (for, while, do-while)                          |   |       |

|    |      | Masking                                                |   |       |

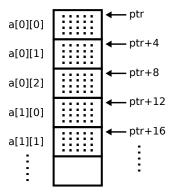

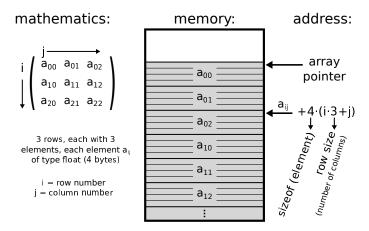

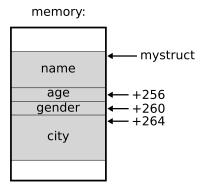

|    |      | Arrays and structures                                  |   |       |

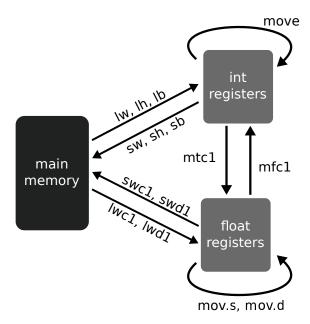

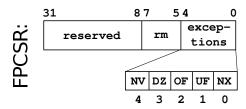

|    |      | Floating point                                         |   |       |

|    |      | Functions and the stack                                |   |       |

|    |      | Macros (pseudo-instructions)                           |   |       |

|    |      | Extensive example: Gauss method for solving equations  |   |       |

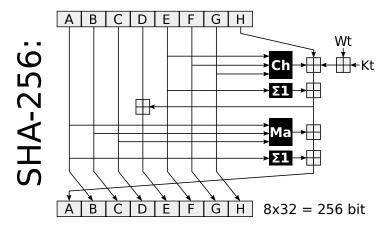

|    | 10.1 | 1Calculating blockchain                                |   | 237   |

CONTENTS v

|              | 10.12RARS: Evolution of MARS                                                                                                                                                                                                                                                                                                                |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

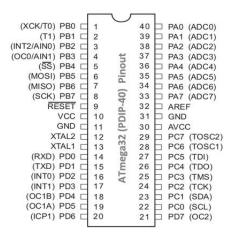

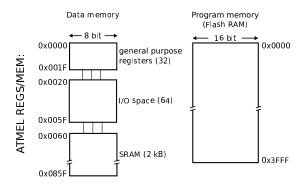

| 11           | Examples of architectures       251         11.1 Difference Engine of Charles Babbage       252         11.2 Intel 4004       253         11.3 MOS 65xx       257         11.4 Atmel AVR       266         11.5 Intel x86       272         11.6 Advanced architectures: Quantum computing and asynchronous (clockless) computing       282 |

| $\mathbf{A}$ | Intel 4004 instruction set                                                                                                                                                                                                                                                                                                                  |

| В            | MOS 65xx instruction set                                                                                                                                                                                                                                                                                                                    |

| $\mathbf{C}$ | AVR Atmel instruction set                                                                                                                                                                                                                                                                                                                   |

| D            | x86 instruction set                                                                                                                                                                                                                                                                                                                         |

| $\mathbf{E}$ | x86 BIOS, MS-DOS and API and Linux interrupts 303                                                                                                                                                                                                                                                                                           |

| $\mathbf{F}$ | Linux (Debian) system calls                                                                                                                                                                                                                                                                                                                 |

| $\mathbf{G}$ | MIPS instruction set                                                                                                                                                                                                                                                                                                                        |

| н            | MARS (MIPS) Assembler directives                                                                                                                                                                                                                                                                                                            |

| Ι            | (MARS) MIPS system calls                                                                                                                                                                                                                                                                                                                    |

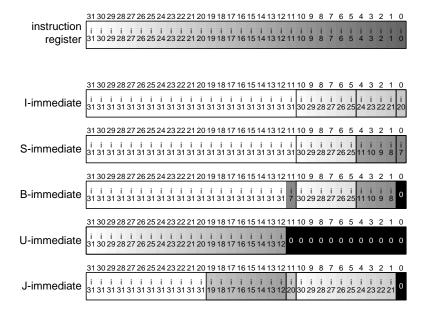

| J            | (RARS) RISC-V base integer instruction set (RV32I) 321 $$                                                                                                                                                                                                                                                                                   |

| K            | (RARS) RISC-V system calls                                                                                                                                                                                                                                                                                                                  |

| ${f L}$      | ASCII                                                                                                                                                                                                                                                                                                                                       |

| i            | Index                                                                                                                                                                                                                                                                                                                                       |

## 1 Introduction

Where does the word computer come from? In spite of what we may think, that it is a very modern word, it actually comes from the 17th century. It derives from the word 'compute' which is from the Latin for 'reckon with' (from the prefix com- and the verb putare meaning to reckon). The word architecture is then derived from the Greek archi + tekton, a builder or craftsman. Computer Architecture is then described as "A fundamental underlying design of computer hardware, software, or both". Indeed, that is what we will describe here in this book. The design of a computer hardware and software and the interplay between them. It has three basic parts: Digital systems, computer hardware, and assembly programming.

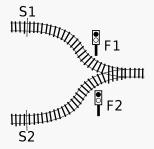

This book is part of a course of Computer Architecture at the first year of a university. It ranges from the number system and then goes from hardware all the way up to programming it in machine language and finally assembly. To start with this point, assembly: While mainly talking about general concepts, explains a specific assembly language designed for a specific architecture, namely MIPS, which for didactic purposes is perfect in that it is a RISC-type architecture (reduced instruction set computer) which thus has a limited amount of instructions. Less is more, because we learn how to see the computer as a machine that constantly shoves information around, like a train engineer shunting wagons in a railway depot.

But where does all this fit in? In the great hierarchy of knowledge. Up front it has to be said that it is assumed here that the reader is comfortable with high-level programming languages. Specifically, for the part on Assembly it is assumed that the reader knows the basic concepts of the C programming language, such as:

- Data types

- Variables and constants

- Comment

- Input/output (printf, scanf)

- Branching: If, if-else and switch; conditional execution

- Loops: for, while, do-while

- Arrays and structures

- Functions (and recursivity)

- Passing by value and passing by reference

- Pointers

Especially the last item — pointers — is very important because basically everything in Assembly is pointers, as we will see. We will also see that nearly all concepts of the list above are not part of Assembly. There are no functions. There are no arrays and structures. Variables do not exist. No looping instructions exist. These are all concepts of the level above, high-level programming languages. In the level below, all these concepts have to be implemented by us ourselves, but we will see that MIPS Assembly is already prepared to implement these concepts and we will learn how to implement them one by one. We will conclude that the link between C and assembly is quite strong. One can even say that, in a way, C is Assembly with macros.

Now the main question is, *why* should we want to learn to write programs in Assembly, if we already know how to program in a higher-level programming language?

- Understanding the level below makes us write code in the level above better. For example, if we know from Assembly that divisions are slower compared to multiplications, we might want to replace a C instruction a = b/5.0 by a = 0.2\*b. Or instead of a = 2\*b we could use a = b+b, since multiplications are very slow compared to additions.

- 2. In cases where hardware is limited, we are forced to optimize the code to increase *efficiency of using memory space and computing time*. This means going to the low level of Assembly.

- 3. In case no high-level compiler exists for an architecture from C to machine language we have to write it ourselves, in which case the knowledge of Assembly is essential.

If you want to jump to the 'goodies', because you came here only to learn how to program in Assembly, you can directly jump to Chapter 10. But the thing I want to address now is: where does this all fit in? That is, in our knowledge of the universe and in the way we think in general? And how exactly did we wind up programming in Assembly and what will we do with this knowledge? In this chapter some background will be given about

computing and how it fits in the layers of knowledge of a university course of Informatics (information processing).

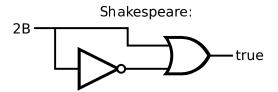

One thing is the information itself, the ideas we are going to process with our hardware. The hard facts — numbers — that we will process to come up with processed information. Maybe the temperature data of the planet processed to come up with a prediction what weather it will be tomorrow. Or maybe an analysis of the stock market to see if we can discern a pattern. This being only monitoring the world, maybe we actually want to use the computer to control the world in things as simple as maintaining the temperature inside a car at a desired value. As we will see in Chapter 2, these 'data' (the numbers) only exist in our heads. What exists in reality is the hardware state, described by electronic properties such as voltages, currents, and charges. The link between the two, the state of the hardware and its behavior on the one hand and the interpretation of that state by concepts in our head, is the realm of Computer Architecture. A gate has 5 volt at its output port, which we interpret as 'true' or '1', etc. The hardware seems to follow the logic in our head. In fact, the hardware is designed to implement the logic we have in our head. A well-designed architecture can efficiently and rapidly process the information in the way we imagined it.

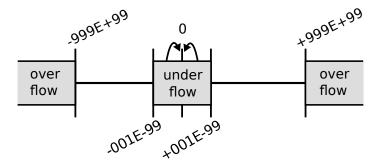

The other thing is the hardware, the physical object that processes our information. The first observation is that it is a so-called finite-state machine, meaning that it can be in one of a limited number of states. This number of states is large, but finite. To give you an idea: a computer with 1 GB of memory has  $2^{8000000000}$  different possible states. Large, but not infinite. The finiteness limitation is especially felt for smaller memory units. The contents of a memory cell or a register in MIPS is 32 bits and this has only  $2^{32}$  different possible states (about 4 billion). This is especially felt when doing floating-point calculations. Whereas in integer calculations ( $\mathbb{Z}$ ) the limitations of our computer being a finite-state machine are to a certain point rather irrelevant and only limit the range of calculations, for floating-point calculations these limitations are severe and we have to keep them in mind. A single 'float' of 32 bits can take only  $2^{32}$  different values, there where the number of real numbers ( $\mathbb{R}$ ) is infinite, even if we were to limit the range of the numbers, for instance only between 0 and 1.

While not inherently necessary, modern computers are all electronic. This means that the state of the machine is defined in terms of electronic properties. It has not always been like that. Imagine, the first automatic processor, the Difference Engine of Charles Babbage in the beginning of the 19th century, was a fully mechanical machine. However, since the 20th century computers are electronic, first with vacuum tubes and later with transistors and integrated circuits (of transistors). We will see primarily such modern machines here.

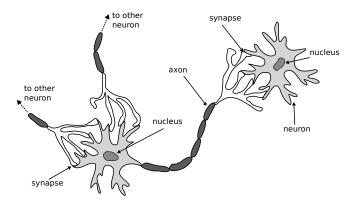

We can thus place this entire thing in the knowledge tree of science. Layers of knowledge of Informatics: The starting layer is Physics. A short while after the Big Bang – so the theory goes – particles were created that consisted of quarks that later condensed into electrons, protons and neutrons. Especially the electrons interest us here. They are charged particles and can thus be manipulated by electrical fields. At this layer of knowledge we speak of Particle Physics, which is not very relevant for an Informatics engineer, but also about the Maxwell Equations, which govern the behavior of the charged particles. And then especially the electrons, which interest us here foremost. While, in principle, we can also make computers using the positively-charged particles, the protons, this is less convenient because protons are about three orders of magnitude heavier than the negatively-charged electrons and 'protonics' is thus expected to be significantly slower than 'electronics'. This layer of knowledge is the realm of Electronic engineers (and physicists alike), but of somewhat less interest for the Informatics engineer.

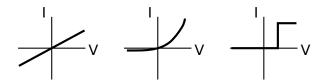

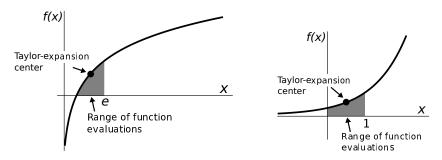

The next layer of knowledge is Electronics. Here we learn concepts of 'current' (which is the movement of charge; how much charge — coulomb — passes a cross-section in space per second) and 'voltage' (which is the amount of potential energy that is stored in a coulomb of charge). We now start suffering here from the most-irritating error ever made by a scientist, namely attributing a negative charge to the electron instead of a positive one. This is so annoying that we always have to imagine that if we have a current from A to B, we have, in fact, a flow of electrons from B to A. That is, if we still want to have some link to the layer of Physics. Most Electronic engineers prefer to make a level of abstraction and just talk about current as if it were a mere mathematical property, forgetting that currents consist of moving electrons. It is possible to get away with this approach, and such abstraction of ignoring underlying levels of knowledge is quite common, as we will see. Electronic engineers now talk about Ohm's law (R = V/I)and power consumption  $(P = V^2/R)$  and the likes. Moreover, they talk about capacitance (C = Q/V) and inductance  $(L = dI/Vdt)^*$ . We can call this level 'linear electronics' since all properties scale linearly: if the voltage increases by a factor 2, the current will also increase by a factor 2, etc. See Figure 1.

This brings us immediately to the next level. If linear electronics exist, also non-linear electronics exist. Actually, here is where it starts getting really interesting. A so-called diode does not have a linear current-voltage relation, but an exponential behavior instead. The current grows exponentially with the applied voltage (or the voltage grows logarithmically with the applied current; for an Electronics engineer it is all the same). This is called

<sup>\*</sup>R is resistance, V is voltage, Q is charge, I is current, C is capacitance, L= inductance, t is time, and  $I=\mathrm{d}Q/\mathrm{d}t$ .

**Figure 1**: Linear electronics, non-linear electronics and digital electronics (I-V curves).

the Ebers-Moll equation, named after two German scientists,

$$I = I_0 \left[ \exp\left(\frac{V}{V_{\mathrm{T}}}\right) - 1 \right].$$

Even more interesting is a transistor, which is a diode with a current-voltage relation between A and B controlled by a third connection, C. The resistance (and current) between A en B is thus controlled by a voltage placed at C, and we thus have a trans-resistor, or 'transistor' for short. An entire world of electronics opened up by the invention of this non-linear behavior. While vacuum tubes — the 'audion' — of De Forest already had this behavior, especially the miniaturization of the transistor made it popular. Signals could be amplified and 'analog' electronics in general surged, for instance radios and televisions. In all these systems the signals are analog in that any value between the supply voltages can exist.

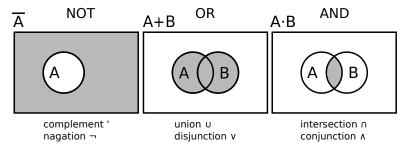

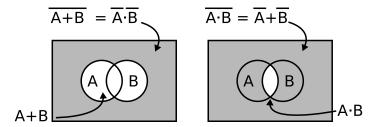

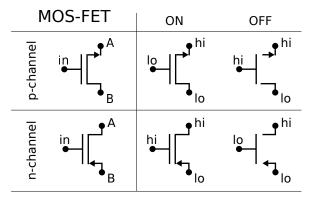

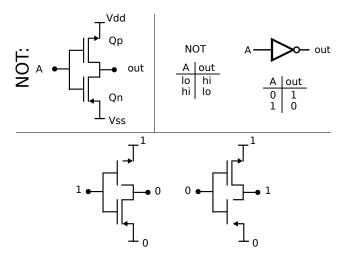

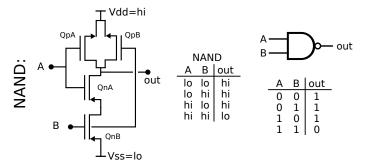

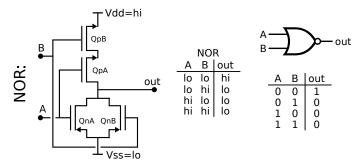

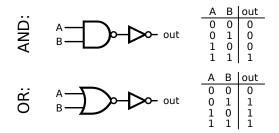

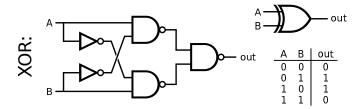

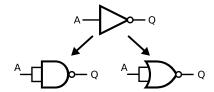

For the Informatics engineers the real fun starts with highly non-linear electronics. By combining transistors in certain ways, circuits can be made that are amplifying so much that basically only two (saturation) states can exist, because the voltages at the output can never exceed the supply voltages (see Figure 1). We can call this 'binary' or 'digital electronics'. We enter the realm of modern Informatics, because we can assign logical values to these two states and process information in a binary, digital way. Moreover, the digital processing of information begins here, because we can make circuits (logic gates) that have two inputs and one output, the output depends on the logical states of the two inputs. We can imagine here OR-gates, NOR-gates, AND-gates, XOR-gates and NAND-gates. Most university courses offer lectures in digital systems, or digital electronics, that treat such systems from the electronics point of view or from the logical point of view. The latter deals with things such as Karnaugh maps to implement any logic based on simple gates, while the former talks about things like CMOS (complementary [channel-type] metal-oxide-semiconductor transistors) to find the most power-efficient implementation of the desired basic logic functions. We see here that this level of knowledge is mixed. It is where Electronic engineers meet with Informatics engineers and they talk about functionality and electronic implementation of that functionality.

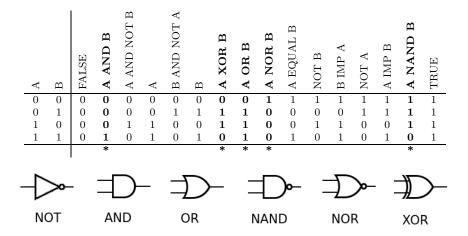

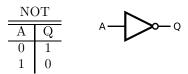

**Figure 2**: The 16 possible 2-input 1-output logic gates (IMP means material implication). Symols for the six fundamental gates. The one-input-one-output inverter (NOT) gate and the five basic two-input-one-output logic gates (AND, OR, NAND, NOR, XOR).

With two input lines and one output line, there are exactly 16 possible logic circuits. Some of them are silly, because they do not depend on any of the inputs (the output always being the logic state 'false' or always the logic state 'true'), or on only one input (copying it, or inverting it), and some of them are redundant (that is, since any functionality can be implemented by, for instance, only NANDs, some gates are redundant). That leaves basically the five logic circuits mentioned above: AND, NAND, OR, NOR, XOR. They are shown in bold and marked with an asterisk in Figure 2.

Note that the names of the devices are what we, humans, give them to somehow make sense out of their behavior. An AND-gate, for example, is named as such because *if* we assume a high voltage is 'true' (written down as '1' here) and applied at both entrances then, and only then, the output voltage is high, meaning 'true' or '1'. We'll get back to this distinction about physical level and logic abstraction later in the coming chapters.

Combining more transistors allows for the implementation of more advanced functionality such as flip-flops (memories), latches, clocks, etc. And also advanced processing circuits such as ALUs (arithmetic and logic units) and even CPUs (central processing units). I would like to refer the reader here to the book of Tanenbaum, *Structured Computer Organization*, where the architecture of computers is very well described.

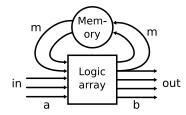

With increased complexity of the functionality more and more transistors are needed. Miniaturization of the transistors made it possible to pack ever more transistors per square centimeter; we all know the famous Moore's law — named after Gordon Moore — that predicts that the number of transistors per area doubles every 2 years, a speed of innovation that is still going on in 2021. We have reached a level of integration that is some tens of billions of transistors on a single 'chip'. Some very powerful circuits can be built with so many transistors and it no longer makes sense of talking about individual gates, let alone transistors. We must make another level of abstraction if we want to keep on understanding what is going on in our hardware. Here is where our knowledge layer of Computer Architecture really starts kicking in. A central processor has several input lines and output lines. It can be imagined as a logic array where we have two sets of input data elements, and one set of lines that define the functionality selected. We can recognize here information as data and a 'program', which consists of supplying a combination of functionalities to actuate on the data.

In the first approach, in the early days, the program and data were supplied to the processor in the form of logic states at the entrance of the processor, for instance mechanical switches supplying voltages 'high' and 'low'. We can represent such programs symbolically by 0s and 1s. The work of an engineer was to translate desired functionality into a set of 0s and 1s to be supplied to the machine. We call such programs therefore 'machine language'. A program for calculating the product of two floating point numbers might be

#### 010001100000001 0001000011000000

Of course, this is hardly legible to the engineer and mistakes must have been quite frequent. One engineer must have coined the idea that doing such repetitive work — it often consisted of doing the same translations of a human-readable logic program to a machine readable machine language — might actually be done by the machine itself. (Take that for a machine making machines). While at first the idea was considered ludicrous — "Why having the machine do something that can perfectly be done by a human being?!" — the paradigm of computing must have shifted from doing as little as possible by the computer to doing as much as possible by the computer. In the 21st century we say, "Why have a human doing work that can perfectly be done by a computer?!" The idea of a 'compiler' or 'translator' was born. The machine running a program (written in machine language, of course) was fed human-readable 'code' that was translated into machine-readable machine-language code and then ran.

The first versions of these meta-languages were still rather close to the machine language and only mnemonics were used for the 'instructions' (functionalities selected). So, the machine code for adding two registers '01110111' was written as add, or something like that. This type of programming

is called second-generation programming languages, or (macro) 'assembly', exactly the layer of knowledge included in this book. It is a level of programming quite close to the hardware level. (There can also be a level of programming inside the ALU and the control logic, which is called micro-assembly, which will not be covered by this book).

Of course, the hierarchy of Informatics does not stop here, but at this point it is nice to take a look back at where we have arrived. Basically, by writing the code 'add', etc., we control the flow of electrons in our processor. Of course, in no way is it necessary for an Informatics engineer to know that electrons are flowing in the processor. The only thing an engineer needs to know is the functionality of the machine and not how it is implemented. An Electronics engineer needs to know about what is going to be done with the electronics, as well as knowing how to implement it in the Physics layer. A Physics graduate is basically just doing philosophy and could not care less what is being done with the knowledge acquired. No scientist — that would be J. J. Thomson — ever thought, "Let me discover the electron, so that we can add two numbers fast".

The engineers soon must have discovered that very often the same functionality was implemented in this assembly. It was always things like forloops, or if-then-else structures. People must have started writing programs in meta-assembly, nearly English. Programs were designed by the well known fluxograms, then written down in English, as in something like

```

for (i=0; i<10; i++){

if (i % 2 == 0)

printf("even");

else

printf("odd");

}</pre>

```

which would then be translated by an engineer into Assembly and fed to the computer. Well, they must have thought, if Assembly can be translated into machine-language by the machine, why not let the machine translate the near-English-source code directly?! This created the so-called third-generation programming languages, of which FORTRAN (Formula Translator), BASIC (Beginners All-Purpose Symbolic Instruction Code), Pascal (named after French Mathematician Blaise Pascal), FORTH (supposed to have been a FOuRTH generation language; at the time commands could only be five letters), and C are the most famous. This is normally the starting level in Informatics of the engineer and scientist alike. It is well possible to never look back at the levels below, but learning assembly is useful for the reasons given earlier.

After having learned high-level 'imperative' programming, students then normally go on and learn to write in object-oriented languages such as C++, Delphi, or Java. Obviously, this now falls way outside the realm of Computer Architecture and the subject of this book. Even more distanced are the sub-

jects of applications such as writing in 'frameworks', where several different programming languages can be joined. As an example may serve Android Studio, that combines writing in Java, HTML (XML) and Javascript all in one IDE (integrated development environment). But don't forget that when you are connecting to Facebook on your mobile telephone, that it is all based on object-oriented programming, that is based on third-level programming languages, that are based on assembly, that is based on machine language, that is based on integrated logic circuits, that is based on non-linear electronics, that is based on electronics, that is based on physics. At the end, it is all because of the Big Bang. So the story goes.

## 2 Number systems

We all use number systems in daily life. The most famous in modern world is the one based on the number 10, the so-called decimal system. The first myth is that this is a very adequate number, because it is nice 'round'. However, note that *any* number, when expressed in that base is written as 10. For example, in the binary system (base 2), 2 is written as ...10.

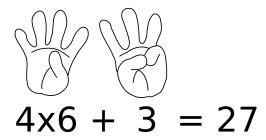

The second myth is that 10 is good for a base system because we have ten fingers. Well, if the number of fingers were to determine what number system to use, it would be 6 or 11. To show why this is: Imagine each hand shows a digit, for instance your left hand shows the units and your right hand the multitudes of 6. You can start counting: decimal=RL (right hand, left hand):

```

1=01,\ 2=02,\ 3=03,\ 4=04,\ 5=05,\ 6=10,\ 7=11,\ 8=12,\ 9=13,\ 10=14,\ 11=15,\ 12=20,\ 13=21\dots

```

and so forth. This is very convenient. A base-6 hexal number system works very well when communicating with your hands, see Figure 3 for an example of how to represent 27 (base 10) with our hands (base 6). So: *five* fingers per hand implies that base-*six* is ideal. Probably for this reason the base-6 number system survived for a long time, with England being the most famous case, since most people in the world have two hands with five fingers each.

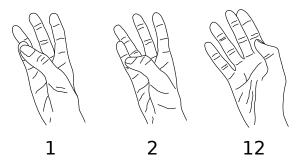

In some cultures also a system of tallying with hands is used that can count up to 12 (or 24). Take your right right and count with your thumb placed on the top phalanx of your little finger (1), then on its middle phalanx (2), then on its bottom phalanx (3). Then continue on the top phalanx of the ring finger (4), etc., until you reach the bottom phalanx of your index finger (12). You can now repeat the process on your left hand (from 13 to 24). While not good for counting, it is very useful for tallying and it does not need any external hardware.

The disadvantage of low-number bases such as the hexal system is that numbers get large faster. That is, they rapidly start having many digits. To give an example, nearly 1 million (999 999) in the decimal system has 6

**Figure 3**: An example of the hexal (base 6) number system with counting on our hands. One hand is used for the units and the other hand for the multiples of the base number 6.

**Figure 4**: Tallying with the 12 phalanxes of the four fingers of your hand, selected by the thumb. Here shown the numbers 1, 2 and 12.

digits while in the hexal system it has 8 (33 233 343).

Other number systems that were popular were base-20. This unit is called a 'score' in English. Take for example this funny Limerick (author unknown):

A Dozen, A Gross, And A Score,

Plus Three Times The Square Root Of Four,

Divided By Seven,

Plus Five Times Eleven,

Equals Nine Squared Plus Zero, No More.

(A dozen is 12, a gross is a dozen dozens,  $12 \times 12 = 144$ ). Some languages still remind us of this score-based system. French speak of quatre vingts for eighty, giving a calculation in the number  $80 = 4 \times 20$ . Likewise, the Danes talk of tres and firs to indicate sixty (=  $3 \times 20$ ) and eighty (=  $4 \times 20$ ), respectively. Confusingly, other Danish numbers are based on the decimal system: tyve (20), tredive (30), fyrre (40). And halvtreds does not mean half tres (60/2=30), but halfway 40 and 60, thus 50. Are you still following it? Well, the Danes seem capable of seeing the logic.

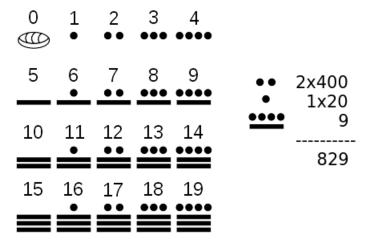

**Figure 5**: The number system of the Mayas based on scores (20). Their unit was represented by a dot, with five of them written as a horizontal bar. The numbers 0 to 19 are shown here. Subsequent digits were stacked vertically on top of each other. An example is the number 829 (=  $2 \times 20^2 + 1 \times 20^1 + 9 \times 20^0$ ) would be written as two dots above one dot above four dots and a bar. Curiously, they also had a symbol for the number zero, probably because the stacking method requires it.

Interestingly, also the Mayas used this system of scores, see Figure 5. A unit was represented by a dot and five dots was written as a horizontal bar. Subsequent units, multiples of the base number 20, were stacked on top. In this way, the number  $829 (= 2 \times 20^2 + 1 \times 20^1 + 9 \times 20^0)$ , for example, would be written as two dots above one dot above four dots and a bar. Note that they also had a symbol for zero, which was needed by their stacking method. How else could one distinguish between 801 (two dots on top of a dot) and 41 (two dots on top of a dot)?

Now, for all you conspiracy thinkers — those that believe in aliens — the question arises how two distinctly separated civilizations (the Mayas and the Danes), that had no contact with each other (since they were separated by the Atlantic Ocean), both seemingly independently decided on 20 for their number system? The answer is that the 20-base is a very natural outcome if you want to do calculations, because it is a number that is divisible by 2, 4, 5 and 10.

The best system was then probably invented by the Babylonians. They used a combination of base 10 and base 6, and this makes it divisible by 1, 2, 3, 4, 5, 6, 10, 12, 15, 20, and 30. That is especially useful when doing divisions with results after the floating point, or with a remainder as we learned in primary school. Compare for example the difficulty of our

| <b>7</b> 1   | <b>∢7</b> 11   | <b>∜7</b> 21    | <b>{{{7}}</b> 31 | <b>₹</b> 7 41    | <b>₹₹7</b> 51     |

|--------------|----------------|-----------------|------------------|------------------|-------------------|

| <b>77</b> 2  | <b>√77</b> 12  | <b>4(77</b> 22  | <b>((17)</b> 32  | <b>12 77</b> 42  | <b>12 PP</b> 52   |

| <b>үүү</b> 3 | <b>(777</b> 13 | <b>4(777</b> 23 | <b>(((7))</b> 33 | <b>44 777</b> 43 | <b>12 m</b> 53    |

| <b>77</b> 4  | <b>(57</b> 14  | <b>(177</b> 24  | <b>****</b> 34   | <b>44</b>        | <b>144 197</b> 54 |

| <b>777</b> 5 | <b>(</b> ) 15  | <b>(177</b> 25  | <b>****</b> 35   | <b>₹</b> ₩ 45    | <b>***</b> 55     |

| <b>777</b> 6 | <b>∜</b> ₩ 16  | <b>****</b> 26  | ₩₩ 36            | <b>₹</b> ₩ 46    | <b>****</b> 56    |

| <b>3</b> 7   | <b>17</b>      | <b>((*)</b> 27  | <b>##</b> 37     | <b>47</b>        | <b>144 89</b> 57  |

| 8            | <b>18</b>      | <b>((A)</b> 28  | ₩₩ 38            | <b>₹</b> 48      | <b>12</b> 58      |

| <b>7</b> 9   | <b>(##</b> 19  | <b>4</b> 7 29   | <b>***</b> 39    | <b>49</b>        | <b>***</b> 59     |

| <b>4</b> 10  | 20             | ₩ 30            | 40               | ₩ 50             |                   |

**Figure 6**: The Babylonian number system based on 10 and 6. A zero was represented by a space, some place without any symbol. (Source: Wikipedia).

decimal system to write out 1/3. It gives a result with an infinite number of digits, 0.3333... (=  $3/10 + 3/10^2 + 3/10^3...$ ). While for the Babylonians, 1/3 is simply 20/60, or a single digit '20' after the floating point.

Note that our geometry and timing are still done in the Babylonian number system. Especially here you can see the power of this number system. A full  $360^{\circ}$  circle can be divided into 2 angles of  $180^{\circ}$ , 3 angles of  $120^{\circ}$ , 4 angles of  $90^{\circ}$ , 5 angles of  $72^{\circ}$ , 6 angles of  $60^{\circ}$ , 8 angles of  $45^{\circ}$ , 9 angles of  $40^{\circ}$ , 10 angles of  $36^{\circ}$ , 12 angles of  $30^{\circ}$ , 15 angles of  $24^{\circ}$ , 18 angles of  $20^{\circ}$ , 20 angles of  $18^{\circ}$ , 24 angles of  $15^{\circ}$ , 36 angles of  $10^{\circ}$ , 40 angles of  $9^{\circ}$ , 45 angles of  $8^{\circ}$ , 60 angles of  $6^{\circ}$ , 72 angles of  $5^{\circ}$ , 90 angles of  $4^{\circ}$ , 120 angles of  $3^{\circ}$ , 180 angles of  $2^{\circ}$ , and 360 angles of  $1^{\circ}$ .

Maybe the worst number system was invented by the Romans. (Makes you wonder how they could be so crafty and build bridges and roads everywhere). The problem with their system is that it does not have a unique base number, nor does it follow the method of ordering the significance of the digits, as for instance is done by the Mayas (highest significant digit on top) or by modern counting (most-significant digit on the left). The Romans had mixed significance, as we all know. Placing a small unit before a large unit puts a negative weight on it. Where 'I' indicates 1 and 'C' stands for 100 (clearly bigger), 99 is represented by placing the I before the C and 101 by placing the I after C. Moreover, the concept of digits (units multiplied with a base raised to some power) does not even exist. It creates a system where the same number can be represented in more than one way. As an example, 99 can also be written as XCIX, which is -10+100-1+10. Digits

in Roman are:

I: 1 V: 5 X: 10 L: 50 C: 100 D: 500 M: 1000

#### Examples:

```

2018 = MMXVIII = 1000 + 1000 + 10 + 5 + 1 + 1 + 1

2019 = MMXIX = 1000 + 1000 + 10 - 1 + 10

```

This Roman system we had better forget as soon as possible. Instead, more useful are standard sign-magnitude number systems:

- Digits have weight. The most-significant digit is on the utmost left, the least significant digit on the utmost right.

- Each step to the left has a weight that is increased by the base number and each step to the right the weight is reduced by a factor equal to the base number.

- Negative numbers are indicated by a preceding '-' sign. Positive numbers can (but don't have to) be preceded by a '+' sign. Alternatively, numbers can be limited to positive, unsigned, values only.

This is all a matter of *conventions*, and at school these conventions are hammered into our heads in such a way that we think it is the only way to do things. Maybe you did not even think it was possible to have a binary system until you were in secondary school. Or any base-number system. In any case, the most common convention is one in which the position of the number determines its weight, as presented above. As an example, if the number base is x, then the number represented by

$\pm abcde_{\rm x}$

is

$$\pm(a\times x^4+b\times x^3+c\times x^2+d\times x^1+e\times x^0).$$

For example,  $12345_6 = 1 \times 6^4 + 2 \times 6^3 + 3 \times 6^2 + 4 \times 6^1 + 5 \times 6^0 = 1865_{10} = 0 \times 10^4 + 1 \times 10^3 + 8 \times 10^2 + 6 \times 10^1 + 5 \times 10^0$ , where the convention was used to write the base as a subscript. In modern times the most-often used convention is base-10 for humans and base-2 (binary) for computers. Let's analyze the latter in detail now.

#### 2.1 Binary numbers

"There are 10 types of people: Those that know binary and those that don't!"

The most important of all number systems for informatics is base-2, simply called 'binary'. That is because the underlying hardware works with binary-state electronics. Any output of any gate can be either low or high. Any capacitor is either full or empty. It does not matter at this moment which one we will ascribe to the logic (sic) '1' and which one to a logic '0'. Now, if we have a set of transistor circuits, each in a certain state designated by '1' or '0', we can *imagine* that they represent a binary number. The number does not really exist in the computer!

Now, this needs some explanation. How can it be that numbers do not exist in the computer? Well, it can be said even stronger: numbers do not exist in the world! They only exist in our heads. They are part of mathematical — that is, imaginary — worlds. The only things that exist in reality are things that are in the realm of Physics, and all physical things can be expressed in terms of the seven basic SI units (kilogram, meter, second, ampere, mol, candela, kelvin) or their derivatives. If it does not have a unit in SI it does not exist. Do not confuse a number with a quantity which has unit 'mol'. If there are two people in the room, in fact there are  $2.0/N_{\rm A}$  mol people in the room, with  $N_{\rm A}$  the number of Avogadro,  $N_{\rm A} = 6.022 \times 10^{23}/{\rm mol}$ .

Likewise, if we have a number (binary or hexadecimal, or whatever) in a computer, what we in fact have is merely a set of gate states (as in high voltage or low voltage; the unit  $V = kg \cdot m^2 \cdot s^{-3} \cdot A^{-1}$ ) that we can – in our heads! – represent with a number. To show why this makes sense: the same combination of gate states, for instance a 32-bit register, can simultaneously be thought of as a binary number, a decimal integer, an ASCII character, or a single-precision floating point number, depending on the *interpretation* of the bit pattern.

The reason why it is useful to do this abstraction is that, if we assume these to represent numbers, the logic of the hardware (ALU, arithmetic and logic unit) follows exactly the logic we have in our heads of how it should behave if they are numbers. The behavior of our computer is consistent with the model in our heads. We are thus able to think as a computer, or a computer 'thinks' the same way we do. The computer implements our thinking, and does it, in contrast to us, flawlessly and rapidly.

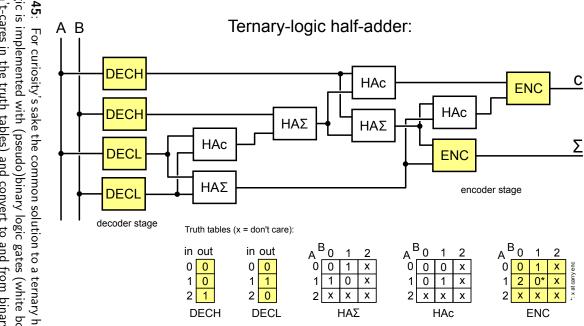

Returning to the subject, binary numbers are very useful in informatics because the gates work with two possible states. Note that it is not obligatory for computers to use this technology. Russians are famous for having developed ternary-logic computers based on gates that have three

possible states, and trits instead of the more common binary logic (two possible states, bits). Apparently, it had some advantages, such as lower power consumption and lower production cost (this according to Wikipedia). Obviously, for such computers, it makes much more sense to represent the information as ternary numbers. However, this technology has died out and we will no longer refer to it here. Rests to say that all logic and all computation could also theoretically be done in ternary-gate electronic computers.

What we have to remember, however, at this point is that there is a symbolic link between a physical set of gate states, the binary representation, and the non-binary interpretation of what information is, in fact, stored there. For example, for a 4-bit gate output we might have the following representations:

Physical levels:

5 volt, 0 volt, 5 volt, 5 volt

Boolean logic levels (assuming false is low voltage, true is high voltage):

true, false, true, true

Binary logic levels (assuming '0' is low voltage, '1' is high voltage):

'1', '0', '1', '1'

Binary value (assuming 0 is '0' and 1 is '1'):

1011

Decimal value (assuming binary value is unsigned int with MSB left):

1 1

Hexadecimal value (idem):

В

With only the first (physical) level really existing and the other just figments of our imagination. Note that it is here assumed that high voltage = true = '1' = 1. In any step this assumption can be different, as in, for instance, high voltage = 'false'. As long as the behavior of the hardware is consistent with the symbolic translation, it is correct. An AND-gate should have a physical behavior that is consistent with the truth table of the logic-AND function, whatever the physical states are.

An important observation to make here: A combination of n binary gates — or n 'bits' — can take  $N=2^n$  different possible 'values' or output combinations. Reasoning the other way around: we need at least  $n=\log_2(N)$  bits (gates) to represent a number that has N possible values. So, for instance, with 3 bits we can 'store' integer numbers from 0 to 7. (Or from 27 to 34, if we'd want that). Reasoning the other way around, to store the 26 letters of the English alphabet, we need at least  $\log_2(26)=4.7$  bits. That is, 5 bits, since partial bits do not exist.

An 8 bit register or memory address can thus store  $2^8 = 256$  different values. If they are unsigned integers including zero, they'd span from 0 to 255. If we represent them in binary, the rightmost bit, the least-significant bit (LSB) has weight  $2^0 = 1$  and the leftmost bit, the most-significant bit

| Decimal | Binary | Hexadecimal  | Octal | BCD |

|---------|--------|--------------|-------|-----|

| 0b      | 0d     | 0x           | 0o    |     |

| 0       | 0000   | 0            | 0     | 0   |

| 1       | 0001   | 1            | 1     | 1   |

| 2       | 0010   | 2            | 2     | 2   |

| 3       | 0011   | 3            | 3     | 3   |

| 4       | 0100   | 4            | 4     | 4   |

| 5       | 0101   | 5            | 5     | 5   |

| 6       | 0110   | 6            | 6     | 6   |

| 7       | 0111   | 7            | 7     | 7   |

| 8       | 1000   | 8            | 10    | 8   |

| 9       | 1001   | 9            | 11    | 9   |

| 10      | 1010   | A            | 12    | -   |

| 11      | 1011   | В            | 13    | -   |

| 12      | 1100   | $\mathbf{C}$ | 14    | -   |

| 13      | 1101   | D            | 15    | -   |

| 14      | 1110   | ${f E}$      | 16    | -   |

| 15      | 1111   | $\mathbf{F}$ | 17    | -   |

**Table I**: Look-up table for binary, hexadecimal, octal and BCD.

(MSB) has weight  $2^7 = 128$ . Likewise, 32-bit registers store integer numbers ranging from 0 to 4,294,967,295. As an example for a 4-bit unsigned integer:

$$1101 = 1 \times 2^3 + 1 \times 2^2 + 0 \times 2^1 + 1 \times 2^0 = 8 + 4 + 0 + 1 = 13.$$

### 2.2 Octal, hexadecimal and binary-coded decimal

The hexadecimal number system is very often used in informatics. It is ubiquitous for a very simple reason already mentioned above: it is simply joining 4 binary bits and attributing a symbol to it. This for a very simple and unique reason: to save space. Hexadecimal is simply shorthand binary. So, we have the simple look-up table as in Table I.

In this table, the A does not represent the letter A of the English alphabet, but rather the bit combination 1010 written in hexadecimal. (As we will see in a moment, the letter 'A' in the English alphabet is coded in ASCII in a different way). To indicate that we are dealing with hexadecimal, instead of writing the 16 subscript after the number (something that is difficult to do in ASCII texts), the number is often preceded by 'zero-x',

0x, as in 0x1AC3, which is  $1 \times 16^3 + 10 \times 16^2 + 12 \times 16 + 3 = 6851_{10}$ . This can also be written as 0d6851, which is the exact same thing. With the same convention, binary numbers are often preceded by 0b, although less frequently used in writing code. Even less used are 0o for octal and 0d for decimal. The 0d is redundant, since decimal is considered default.

To convert hexadecimal to and from binary is very easy. As the table shows, every hexadecimal digit is equivalent to four binary digits. Thus we can write out hexadecimal by replacing every digit by its corresponding 4-bit equivalent. Likewise, binary numbers are converted to hexadecimal by grouping the binary digits in sets of 4 bits and looking up in the table what hexadecimal digits they are. An example: 0xA3 is 1010 0011 in binary. And 0b1001 1101 0100 0001 is 0x9D41.

The same trick we can also use for octal numbers. A single octal digit is converted to three binary digits, ranging from 000 (octal 000) to 111 (octal 007). An example,  $375_8$  (00375) becomes 011 111 101. Converting to octal is done by grouping in sets of three bits (with optional adding of zeros in front if needed), and looking in the table. As an example, 0b11101001 is converted into 00351.

The table also shows binary-coded decimal (BCD), which is similar to hexadecimal with the last combinations not used. However, a computer calculating in BCD is not the same as a computer calculating in binary (and thus hexadecimal). As an example, in BCD, 07+07=14: or 0000 0111+0000 0111=0001 0100, while in binary or hex it is 00000111+00000111=00001110, or 0x07+0x07=0x0E. As can easily be shown, binary calculations are more efficient in computers but are further away from human thinking, and this is the reason why earlier architectures often use decimal or binary-coded decimal.

#### 2.3 Arithmetic

This part may seem a little odd. To talk about how to do arithmetic in the decimal system, while this is exactly what we have already learned very well in primary school. But, in spite of us having learned it well, perhaps we did not realize what the underlying method was. What algorithm we used for arithmetic? More specifically for adding, subtracting, multiplying and dividing. We will see that these algorithms can be used in any number system, including binary. They are based on us memorizing (burning in our hardware, our minds) some simple tables and executing simple operations. We make here one simplification in that we use only two-operand arithmetic (although we have learned to do multi-operand additions  $A+B+C+\ldots$  in school).

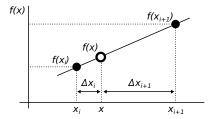

Let's start with addition, Z = A+B. We perform additions of multi-digit numbers by doing addition one digit at a time. As an example, adding 714

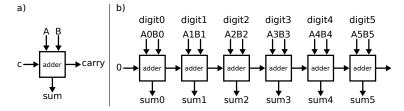

**Figure 7**: a) A single-digit adder implementing a table such as the one shown in Table II and Table IV for decimal and binary. b) How this hardware can perform a multi-digit addition.

to 888: We start with the least significant digits and add them. 8 plus 4 is 12. Houston, we got a problem, 12 is not a single digit and we have an overflow. We have learned to deal with this by just keeping the last digit and remembering the overflow digit '1', which we call a 'carry'. Now this carry is then carried over to the next digit summation, which now is 8+1+carry which gives 0 plus a new carry. We get this result from the very simple memorized addition table (see Table II) that includes such carry-ins and carry-outs. Our addition becomes (white spaces are considered 0)

$$\begin{array}{ccc} 1 \ 1 \ 1 \ 0 & carries \\ 8 \ 8 \ 8 & operand \ A \\ \hline 1 \ 1 \ 0 \ 2 & operand \ B \ + \\ \end{array}$$

Note that we start with the carry-in of the least significant digit always equal to 0. Note also that the carry cannot be larger than 1 for bi-operand additions. At most we can have an addition of 9+9+carry=19 which will give 9 with a carry of 1 as output. This statement is valid for additions in any number system.

When we design a computer, all we need is some hardware that somehow has this addition table burned in and the algorithm programmed in. We could of course also have burned in all possible sums of any integers A and B up to a certain amount of digits, but that is becoming rapidly extensive (and expensive) hardware. Moreover, it is not very flexible. Up to how many digits are we going to burn it in hardware? Two? Three? A hundred? We just prefer to do the simple table in hardware and the rest in the algorithm, with some useful tricks here and there (see Table III).

Now let's look at how additions work in binary calculations. The idea is the same, but obviously the table is much simpler, see Table IV. An example, adding 110 to 011 becomes

2.3. ARITHMETIC 21

**Table II**: Addition table for decimal numbers. As an example, adding 6 (row 6) to 6 with a carry ("c" in column 6) gives a sum of 3 with a carry out (carry) equal to 1, shown in bold font.

|   | 0 c | 1 c | 2 c | 3 c | 4 c | 5 c | 6 c        | 7 c | 8 c | 9 c |       |

|---|-----|-----|-----|-----|-----|-----|------------|-----|-----|-----|-------|

| 0 | 0.1 | 1 2 | 2 3 | 3 4 | 4 5 | 5 6 | 6 7        | 7 8 | 8 9 | 9 0 | sum   |

|   | 0 0 | 0 0 | 0 0 | 0 0 | 0 0 | 0 0 | 0 0        | 0 0 | 0 0 | 0 1 | carry |

| 1 | 1 2 | 2 3 | 3 4 | 4 5 | 5 6 | 6 7 | 7 8        | 8 9 | 9 0 | 0.1 | sum   |

|   | 0 0 | 0 0 | 0 0 | 0 0 | 0 0 | 0 0 | 0 0        | 0 0 | 0 1 | 1 1 | carry |

| 2 | 2 3 | 3 4 | 4 5 | 5 6 | 6 7 | 7 8 | 8 9        | 9 0 | 0 1 | 1 2 | sum   |

|   | 0 0 | 0 0 | 0 0 | 0 0 | 0 0 | 0 0 | 0 0        | 0 1 | 1 1 | 1 1 | carry |

| 3 | 3 4 | 4 5 | 5 6 | 6 7 | 7 8 | 8 9 | 9 0        | 0.1 | 1 2 | 2 3 | sum   |

|   | 0.0 | 0 0 | 0 0 | 0 0 | 0 0 | 0 0 | 0.1        | 1 1 | 1 1 | 1 1 | carry |

| 4 | 4 5 | 5 6 | 6 7 | 7 8 | 8 9 | 9 0 | 0 1        | 1 2 | 2 3 | 3 4 | sum   |

|   | 0.0 | 0 0 | 0 0 | 0 0 | 0 0 | 0.1 | 1 1        | 1 1 | 1 1 | 1 1 | carry |

| 5 | 5 6 | 6 7 | 7 8 | 8 9 | 9 0 | 0 1 | 1 2        | 2 3 | 3 4 | 4 5 | sum   |

|   | 0.0 | 0 0 | 0 0 | 0 0 | 0 1 | 1 1 | 1 1        | 1 1 | 1 1 | 1 1 | carry |

| 6 | 6 7 | 7 8 | 8 9 | 9 0 | 0 1 | 1 2 | 2 <b>3</b> | 3 4 | 4 5 | 5 6 | sum   |

|   | 0.0 | 0 0 | 0 0 | 0 1 | 1 1 | 1 1 | 11         | 1 1 | 1 1 | 1 1 | carry |

| 7 | 7 8 | 8 9 | 9 0 | 0 1 | 1 2 | 2 3 | 3 4        | 4 5 | 5 6 | 6 7 | sum   |

|   | 0.0 | 0 0 | 0.1 | 1 1 | 1 1 | 1 1 | 1 1        | 1 1 | 1 1 | 1 1 | carry |

| 8 | 8 9 | 9 0 | 0 1 | 1 2 | 2 3 | 3 4 | 4 5        | 5 6 | 6 7 | 7 8 | sum   |

|   | 0.0 | 0 1 | 1 1 | 1 1 | 1 1 | 1 1 | 1 1        | 1 1 | 1 1 | 1 1 | carry |

| 9 | 9 0 | 0 1 | 1 2 | 2 3 | 3 4 | 4 5 | 5 6        | 6 7 | 7 8 | 8 9 | sum   |

|   | 0.1 | 1 1 | 1 1 | 1 1 | 1 1 | 1 1 | 1 1        | 1 1 | 1 1 | 1 1 | carry |

$$\begin{array}{ccc} 1 \ 0 \ 0 & carries \\ 0 \ 1 \ 1 & operand \ A \\ \underline{1 \ 1 \ 0} & operand \ B \ + \\ \hline 1 \ 0 \ 0 \ 1 & \end{array}$$

The hardware can be much simpler since it needs to remember only 16 values compared to 400 for the decimal adder.

Subtractions can be done by a similar table, but with 'borrows' instead of carries. The reader is invited to design such tables. However, as we will see, there is a much more elegant way of subtractions, and that is to convert the subtraction into an addition of the negative number. As we will see, this is easily done when we use two's-complement representation of numbers, as discussed later in this chapter. For this reason we postpone the discussion of subtractions to a later stage, namely at the place where we design the hardware (Chapter 6).

**Table III**: Some simple calculation 'tricks'

- Multiplying by the base (always written as '10' in that base!) is simply adding a zero at the end of the number. Example: 10 times 53 is 530. We call this operation in computer jargon a 'left-shift'.

- A number which has a sum of digits divisible by 3 is divisible by 3. Example: 7893 has a sum of digits 7+8+9+3=27, which has a sum of digits 2+7=9, which is divisible by 3 and thus 7893 is divisible by 3 (meaning leaving no remainder when dividing by 3). Same trick is for divisibility by 9. Moreover: Divisible by 2 if last digit is divisible by 2. Divisible by 5 if last digit is 0 or 5.

- The square of a two-digit number ending with 0 is the square of the first digit followed by '00':  $(D0)^2 = D \times D$  00. Example:  $40^2 = 16$  00. The square of a two-digit number ending with 5 is the product of the first digit times the first digit plus one and added '25':  $(D5)^2 = D \times (D+1)$  25. Example:  $45^2$ , knowing  $4 \times 5 = 20$ , is 20 25. Generally, a two-digit square (example  $28^2 = 784$ ) can be done in the following way: 1) Add the last digit to the full number, e.g., 28 + 8 = 36. 2) Multiply this number by the first digit and left-shift one case. E.g.,  $2 \times 36 = 72$  0. 3) Add the square of the last digit to this number, e.g. 720 + 64 = 784.

- $9 \times D = (D-1) (10-D)$ . Example for D equal to 8:  $9 \times 8 = 7$  2.

**Table IV**: Addition table for binary numbers. As an example, adding 1 (row 1) to 0 with a carry ("c" in column 0) gives a sum of 0 with a carry out (carry) equal to 1, shown in bold font.

|   | 0 c | 1 c |           |

|---|-----|-----|-----------|

| 0 | 0 1 | 1 0 | sum       |

|   | 0 0 | 0 1 | carry out |

| 1 | 1 0 | 0.1 | sum       |

|   | 0 1 | 1 1 | carry out |

23

| Table V:    | Multiplication  | table for | decimal  | shown | as di | igit pairs | ср, | with c |

|-------------|-----------------|-----------|----------|-------|-------|------------|-----|--------|

| the carry a | and p the produ | ct of the | operatio | n.    |       |            |     |        |

| ×  | 0  | 1  | 2  | 3  | 4  | 5  | 6  | 7  | 8  | 9  |

|----|----|----|----|----|----|----|----|----|----|----|

| 00 | 00 | 00 | 00 | 00 | 00 | 00 | 00 | 00 | 00 | 00 |

| 01 | 00 | 01 | 02 | 03 | 04 | 05 | 06 | 07 | 08 | 09 |

| 02 | 00 | 02 | 04 | 06 | 08 | 10 | 12 | 14 | 16 | 18 |

| 03 | 00 | 03 | 06 | 09 | 12 | 15 | 18 | 21 | 24 | 27 |

| 04 | 00 | 04 | 08 | 12 | 16 | 20 | 24 | 28 | 32 | 36 |

| 05 | 00 | 05 | 10 | 15 | 20 | 25 | 30 | 35 | 40 | 45 |

| 06 | 00 | 06 | 12 | 18 | 24 | 30 | 36 | 42 | 48 | 54 |

| 07 | 00 | 07 | 14 | 21 | 28 | 35 | 42 | 49 | 56 | 63 |

| 08 | 00 | 08 | 16 | 24 | 32 | 40 | 48 | 56 | 64 | 72 |

| 09 | 00 | 09 | 18 | 27 | 36 | 45 | 54 | 63 | 72 | 81 |

Also for multiplications we use an algorithm of reducing it to single-digit operations that are then looked up in a table. The basic bi-operand singledigit multiplication information is shown in Table V. The product and carry entries are here written in double-digit representations cp, with c the carry and p the product of the operation. For example,  $6 \times 6$  gives 36, meaning the result is 6, with a carry of 3.

We can now perform a multi-digit bi-operand multiplication by performing shift-multiply-add operations, a method that is called the Russianpeasant algorithm. Take for example  $238 \times 123$ . We first multiply each digit of the first operand by the last digit (least significant digit, LSD) of the second operand (3),  $238 \times 3$  which gives 714 as can easily be seen (note also the carries): From our look-up table we know that  $3 \times 8 = 24$  (4 plus 2 as carry). Then the next step  $3 \times 3 = 9$  plus the carry is 1 plus 1 as carry. Then, the final step is  $3 \times 2$  is 6. Plus the carry from the previous step is 7. Final result: 714. Remember how we did this in school (the unused digits of operand B at every step put in brackets):

$$\begin{array}{ccc} 1 \ 2 \ 0 & \text{carries} \\ 2 \ 3 \ 8 & \text{operand A} \\ \hline (12)3 & \text{LSD operand B} \times \\ \hline 7 \ 1 \ 4 & \text{intermediate result} \end{array}$$

Then we shift operand A to the left (multiplying effectively by the base 10; adding a 0, thus 2380) and operand B to the right (dividing effectively by the base 10, forgetting the remainder). So, the last digit of operand B is now 2, so we multiply 2380 by 2, and then add the previous result to it:

**Table VI**: Multiplication table for binary. Note: Never a carry occurs.

| × | 0 | 1 |

|---|---|---|

| 0 | 0 | 0 |

| 1 | 0 | 1 |

$$0\ 1\ 0\ 0$$

carries  $2\ 3\ 8\ 0$  operand A  $(1)2$  LSD of operand B  $\times$   $4\ 7\ 6\ 0$  new result  $0\ 0\ 0$  carries  $0\ 0\ 0$  carries  $0\ 0\ 0$  new result  $0$

Once again shift operand A to the left and operand B to the right. So, the last digit of operand B is now 1, so we multiply 23800 by 1, and then add the previous result to it:

| $0\ 0\ 0\ 0\ 0$     | carries                        |

|---------------------|--------------------------------|

| $2\; 3\; 8\; 0\; 0$ | operand A                      |

| 1                   | LSD of operand B $\times$      |

| 2 3 8 0 0           | new result                     |

|                     |                                |

| $0\ 1\ 0\ 0\ 0$     | carries                        |

| $2\; 3\; 8\; 0\; 0$ | new result                     |

| $5\ 4\ 7\ 4$        | previous intermediate result + |

| 29274               | final result                   |

The next shift-right division-by-10 of operand B results in 0 and we have finished our calculation. Final result: 29274.

In binary this algorithm is much simpler. The look-up table for binary numbers is very simple, it can barely be called a table, the output is either 0, if operand B is 0, or equal to operand A if B is 1. There is never a carry! See Table VI. This makes the Russian-peasant algorithm very easy; shift-multiply-add becomes simply shift-add.

An example of a long multiplication by this algorithm in binary is shown here below for multiplying  $A=13\ (1101)$  with  $B=11\ (1011)$ . Note that if the rightmost bit of operand B is 0, no addition has to be done, and if that bit is 1, no multiplication has to be done, the operand A simply needs to be added:

| A                                         |

|-------------------------------------------|

| B. (LSB of B is 1: add A)                 |

| temporary result                          |

| L-shifted A, (R-shifted B=10 1: add A)    |

| temporary result                          |

| L-shifted A, (R-shifted B=1 0: no action) |

| temporary result                          |

| L-shifted A, (R-shifted B=1: add A)       |

| final result $(143_{10})$                 |

|                                           |

No multiplication has to be done in binary. Just shift, mask (seeing if a digit is 1) and add.

#### 2.4 Number conversion

Now the question is, how to convert between number systems? The obvious way is to do the counting in the destination number system. An example is the one given above from hexal to decimal,  $12345_6 = 1 \times 6^4 + 2 \times 6^3 + 3 \times 6^2 + 4 \times 6^1 + 5 \times 6^0 = 1865_{10}$ , with the right side of the equation a decimal calculation. We are very familiar with calculations in decimal, which are fundamentally based on the multiplication tables that were hammered into us at an early age, see Table V. From the expression above it is clear that also the powers n of the source base numbers x, expressed in the destination number system, are useful, see Tables VII, VIII and IX for decimal, pental and binary, respectively. In this case we will need the line with powers of 6 expressed in the decimal system. With this table we can see that  $12345_6$  is

$$\begin{array}{rcl}

1 \times 6^4 &=& 1,296 \\

2 \times 6^3 &=& 432 \\

3 \times 6^2 &=& 108 \\

4 \times 6^1 &=& 24 \\

5 \times 6^0 &=& 5

\end{array}$$

We can also do the calculations in the *source* system. It involves divisions (compared to multiplications above). An example is the division of  $12345_6$  by  $14_6$  in the conversion of base-6 to base-10. In base 6:

```

12345/14 = 510 + 5/14 (remainder is 5_{10})

510/14 = 30 + 10/14 (remainder is 6_{10})

30/14 = 1 + 12/14 (remainder is 8_{10})

1/14 = 0 + 1/14 (remainder is 1_{10})

```

So the number in the decimal system – reading the remainders from the last to the first – is 1865, which is equal to the result found before.

Considering our acquaintance with base-10 calculations, conversions from base-10 to other bases are better done by the latter technique, while con-

| $n \rightarrow$ | 5         | 4          | 3     | 2   | 1  | 0 |

|-----------------|-----------|------------|-------|-----|----|---|

| $x\downarrow$   |           |            |       |     |    |   |

| 2               | 32        | 16         | 8     | 4   | 2  | 1 |

| 3               | 243       | 81         | 27    | 9   | 3  | 1 |

| 4               | 1,024     | 256        | 64    | 16  | 4  | 1 |

| 5               | $3,\!125$ | 625        | 125   | 25  | 5  | 1 |

| 6               | 7,776     | 1,296      | 216   | 36  | 6  | 1 |

| 7               | 16,807    | 2401       | 343   | 49  | 7  | 1 |

| 8               | 32,768    | 4,096      | 512   | 64  | 8  | 1 |

| 9               | 59,049    | $6,\!561$  | 729   | 81  | 9  | 1 |

| 16              | 1,048,576 | $65,\!536$ | 4,096 | 256 | 16 | 1 |

**Table VII**: Some powers  $x^n$  in the decimal system (base 10).

**Table VIII**: Multiplication table and some powers  $x^n$  in the pental system (base 5).

|   | 0 | 1 | 2  | 3  | 4  |

|---|---|---|----|----|----|

| 0 | 0 | 0 | 0  | 0  | 0  |

| 1 | 0 | 1 | 2  | 3  | 4  |

| 2 | 0 | 2 | 4  | 11 | 13 |

| 3 | 0 | 3 | 11 | 14 | 22 |

| 4 | 0 | 4 | 13 | 22 | 31 |

| $n \rightarrow$    | 10          | 4      | 3      | 2    | 1  | 0 |

|--------------------|-------------|--------|--------|------|----|---|

| $x\downarrow$      | $(=5_{10})$ |        |        |      |    |   |

| 2                  | 112         | 31     | 13     | 4    | 2  | 1 |

| 3                  | 2244        | 311    | 102    | 14   | 3  | 1 |

| 4                  | 13044       | 2011   | 224    | 31   | 4  | 1 |

| $11 \ (= 6_{10})$  | 222101      | 20141  | 1331   | 121  | 11 | 1 |

| $13 (= 8_{10})$    | 2022033     | 112341 | 4022   | 224  | 13 | 1 |

| $20 \ (= 10_{10})$ | 11200000    | 310000 | 13000  | 400  | 20 | 1 |

| $31 (= 16_{10})$   |             |        | 112341 | 2011 | 31 | 1 |

**Table IX**: Multiplication table and some powers  $x^n$  in the binary system (base 2).

|                                |          | $\begin{array}{c cccc} & 0 & 1 \\ \hline 0 & 0 & 0 \\ 1 & 0 & 1 \\ \end{array}$ | _       |       |     |   |

|--------------------------------|----------|---------------------------------------------------------------------------------|---------|-------|-----|---|

| $n \rightarrow$                | 101      | 100                                                                             | 11      | 10    | 1   | 0 |

| $x \downarrow 10 \ (= 2_{10})$ | 100000   | 10000                                                                           | 1000    | 100   | 10  | 1 |

| $11 \ (= 3_{10})$              | 11110011 | 1010001                                                                         | 11011   | 1001  | 11  | 1 |

| $100 \ (= 4_{10})$             |          | 100000000                                                                       | 1000000 | 10000 | 100 | 1 |

versions to base-10 are easier done with the former method. Especially, conversions to base-2 are done by successive divisions by 2 (with the remainders in reverse order the resulting bit pattern), and conversions from base-2 are done by successive multiplications by 2 (or powers of 2) and addition. Conversions from base-x to base-y (with x and y both not 10) can also be done by first converting base-x to base-10 and then from base-10 to base y. In this way we make use of our familiarity with base-10 calculations.

Now let's do a more complicated example, from hexal to pental. What is 1234<sub>6</sub> in base-5? We can use the multiplication table and power table from the pental system, Table VIII. The first four powers of six (11) in base-5 are: 1, 11, 121, 1331. So we need to calculate  $1 \times 1331 + 2 \times 121 + 3 \times 11 + 4 \times 1$  in the pental system:

$$\begin{array}{rrrrr}

1 \times 1331 &=& 1331 \\

2 \times 121 &=& 242 \\

3 \times 11 &=& 33 \\

\underline{4 \times 1} &=& \underline{4} \\

&=& 2220

\end{array} +$$

In other words, the answer is  $2220_5$ . Check (by converting both  $1234_6$  and  $2220_5$  to the decimal system,  $310_{10}$ ) that this is indeed correct.

While floating point numbers will be treated in a separate section further on, it should be noted here that conversions after the floating point are done by the opposite operation. So, if we want to convert for instance  $0.8125_{10}$  to binary, we do successive *multiplications* by 2. If the number is larger or equal to 1, we write a 1 (0 otherwise) and continue with the remainder after the floating point. So

$$0.8125 \times 2 = 1 + 0.625$$

$0.625 \times 2 = 1 + 0.25$

$0.25 \times 2 = 0 + 0.5$

$0.5 \times 2 = 1 + 0.0$

and the number is 0.1101 in binary.

Note that in an arithmetic evaluation we can first do the conversion to the new number system, then do the calculation, or first do the calculation and then the conversion. The end result is the same. Even if we do not realize it, this is the basis of computer calculations; they can be done in binary and the result then presented in decimal.

Note also that numbers in the unary system (base 1) are possible. Just as binary digits have two possibilities (0 and 1) and base-n digits in general have n possibilities, base-1 digits have 1 possibility (0). The value of a number is simply the number of 0s in the number. So  $7_{10} = 0000000_1$ . We can no longer use the convention that adding 0s in front of a number does not change its value, though, as it obviously does in the case of base-1 numbers. Nor does floating point make any sense. Unary counting does, however, make sense in payments based on things such as gold; note that every digit in the number has the same weight, similar to the equality of every gold coin in your pocket. It is a tallying system, not a counting system.

#### 2.5 Negative numbers

So far so good. The complications start when we want to interpret the bit patterns to include negative numbers as well and have the hardware capable of dealing with them, that is, having the ALU perform gate operations that are consistent with the formalism of the gate voltages representing numbers that can be positive as well as negative. The problem is that the sign symbol (+ or -), introduced by us before is not directly implemented in hardware, as that has only 0s and 1s, conventionally. So we have to augment our convention.

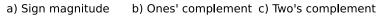

As a first thought, we may think of using — 'sacrificing' — one bit for the sign, and continuing to use rest for the magnitude (which now has a smaller range, 0 unto  $2^{n-1}-1$ ). This scheme is called sign-magnitude. See Figure 8a for a three-bit example. Assuming the above binary combination is a sign-magnitude representation of an integer number, with the MSB representing the sign (0='+', 1='-'), it would give:

1101 =

$$-(1 \times 2^2 + 0 \times 2^1 + 1 \times 2^0)$$

=  $-(4+0+1) = -5$

Note the peculiar property of sign magnitude that there are two numbers zero, namely +0 (0000) and -0 (1000). More problematic is that we can

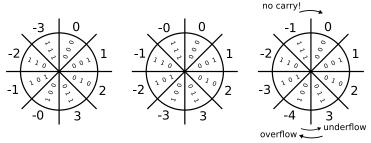

**Figure 8**: Three ways of representing signed numbers; 3-bit examples. a) In sign-magnitude, the MSB is the sign bit, 0 for '+' and 1 for '-', while the rest of the bits form a normal unsigned n-1-bit number. b) In ones'-complement, to find a negative number, simply all bits are inverted. c) In two's-complement, the MSB has a negative weight  $-2^{n-1}$  while the other bits have positive weight  $+2^{n-2}$  to  $+2^0$ .

no longer use the same hardware for these sign-magnitude numbers and the unsigned integer numbers. As an example, imagine adding 1 to -2 using hardware we learned from digital electronics classes:

| bit     |   | unsigned | sign-     |

|---------|---|----------|-----------|

| pattern |   |          | magnitude |

| 0001    | : | 1        | +1        |

| 1010    | : | 10       | -2        |

| 1011    | : | 11       | -3        |

The same problem we have in the alternative ones'-complement. In this scheme, we just invert all the bits to get the negative number, see Figure 8b for a 3-bit example. Like in sign-magnitude, positive numbers start with a 0 and negative numbers start with a 1. Moreover, also here we have two possible ways to represent zero, namely +0 = 0000 (all 0s) and -0 = 1111 (all 1s). While the calculations at first sight seem to be going better, we have this peculiar result that occurs whenever there is a carry:

| bit     |   | unsigned | ones '-    |

|---------|---|----------|------------|

| pattern |   |          | complement |

| 0011    | : | 3        | +3         |

| 1110    | : | 14       | -1         |

| 0001    | : | 1        | +1         |

This can be solved by adding the carry that was ignored. Adding it will make the final result +2, which is correct. However, we would like to use the same hardware for unsigned integer operations and signed integer operations and

not have to resort to additional operations when adding signed integers. The perfect solution for that is the two's-complement representation of numbers.

Two's-complement is formed by giving a negative weight  $-2^{n-1}$  to the MSB, and positive weights  $+2^{n-2}$  to  $+2^0$  to the other bits until the LSB. See Figure 8c for a 3-bit example. The number -1 is thus formed by a combination of all 1s. And this gives another way of rapidly looking at things:

- If the first bit (MSB) is 0, treat the number as a normal unsigned int, with every (other) bit its proper weight. Example, 00000100: The positional weight of the only 1 is 4, therefore the number is +4.

- If the first bit (MSB) is 1, the number is equal to -1 plus every 0 (sic) weighted by its positional weight negatively. Example, 11111011: The positional weight of the only 0 is 4, therefore the number is -1 4 = -5.

This might come in handy sometimes when we want rapid answers. Especially for large bit numbers. (A 32-bit two's-complement int,

####

is also -5).

Note that two's-complement has only one version of zero. It can use the same hardware logic as unsigned integers:

| bit     |   | unsigned | two 's-    |

|---------|---|----------|------------|

| pattern |   |          | complement |

| 0001    | : | 1        | +1         |

| 1010    | : | 10       | -6         |

| 1011    | : | 11       | -5         |

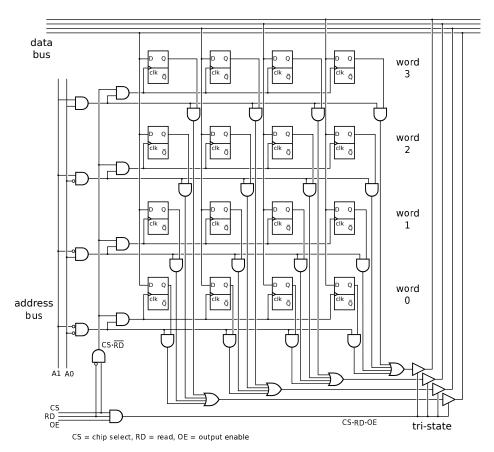

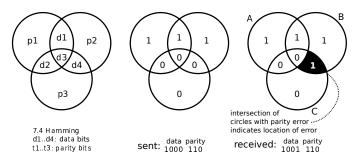

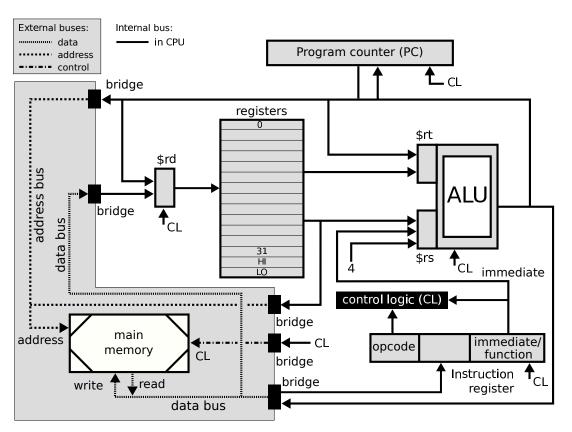

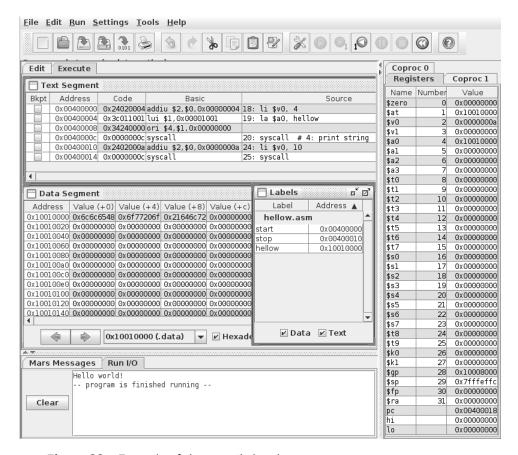

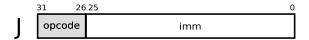

Interestingly, the carry can be ignored (see Figure 8c). On the other hand, a phenomenon occurs halfway the bit pattern, when the MSB changes  $0 \to 1$ ,